This is Part 3 of a Three Part Series

- Chip Resistors Part 1: The Basics

- Chip Resistors Part 2: Types

- Chip Resistors Part 3: Applications and Considerations

Greetings designers! In my last post we discussed several types of chip resistors and applications. In this post, we will discuss some application factors as well as important considerations.

Applications

Resistors are used in numerous applications, such as current sensing, circuit tuning, voltage dividing, gain setting, high frequency terminations and myriad high voltage and high power applications. Many of these applications may also be environmentally challenging, such as high temperature, high sulfur or high humidity atmospheres or the like. This article focuses on the potential effects of precision/matching, frequency, temperature and current as each may be an important factor in your application.

Precision and Matching

In certain applications, it is highly important to use resistors that are well-matched. For example in the non-inverting amplifier circuit (Op-Amp based) illustrated below, the gain (G) is established by the ratio of the resistor values shown through the relation G=1+(R2/R). If a minimum amplifier precision of 1% is required, then the nominal resistance values of resistors R1 and R2 not vary more than +/-0.25%. Further, it is important that the resistors used in this application have well-matched temperature coefficient of resistance (TCR).

For example, using resistors having TCR of 200 ppm/C would result in 1% change in gain (G) if ΔT between them is 50C. This could occur as a result of self heating of R2 for instance, or if one of the resistors is placed too close to a heat source (e.g., high power actives or the like). For high precision systems (say 10 bit, requiring 0.1% G accuracy or better), matching of R1 and R2, combined with use of low TCR (and similar TCR) resistor materials becomes important. Additionally, design that minimizes ΔT between R1 and R2 is important. In these cases, the use of high precision resistors or of matched resistor networks is a common solution. Trimmable resistors may also be valuable in these applications.

Temperature Considerations

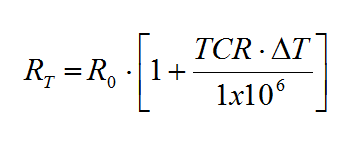

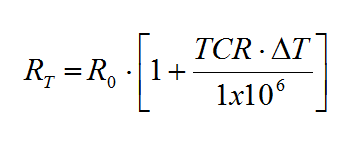

As mentioned above, temperature effects are important for resistors that must be matched, but they are also important in other applications requiring stable resistance. Low TCR is generally preferred, but must be balanced with the economic factors of your design, as low TCR resistors are generally more expensive. The effect of TCR on resistance is calculated using the relation:

where:

- RT is resistance at the temperature of interest (Ω)

- R0 is the nominal resistance (Ω)

- TCR is temperature coefficient of resistance (PPM/C)

- ΔT is the change in temperature from nominal (C),

Indicating that the use of low TCR materials in the resistors that are used in your design is preferred, and that ΔT in your circuit’s operating environment should be kept to a minimum in order to avoid resistance changes in your design.

Additional variation in resistance may result from thermoelectric effects. Chip resistors typically are made from at least two different conductor materials; the resistive element is generally one material and the external terminal material, or the termination, is generally at least one different conductor material. When dissimilar metals are joined, a thermocouple may be formed due to the Seebeck effect. This effect results in the generation of a small voltage between the terminals of the resistor that is based upon the difference in temperature (T) between the terminals. It is similar to the phenomenon that results in a thermocouple output voltage that makes thermocouples useful for measuring temperature. This effect can be significant in precision circuits, so it is important to design your circuit such that ΔT between each chip resistor terminal is minimized (e.g., design such that cooling airflow traverses each resistor terminal equally, or design that avoids placement of one terminal near a heat source, or the like).

Random thermal movement of charge carriers in a resistor element also produces noise that is proportional to the operating temperature, as well as to the use bandwidth, the current and the resistance of the device in a one half power manner. This can become significant as one or more of operating temperature, current, use bandwidth or resistance is increased.[1]

Frequency Considerations

Resistor Parasitics

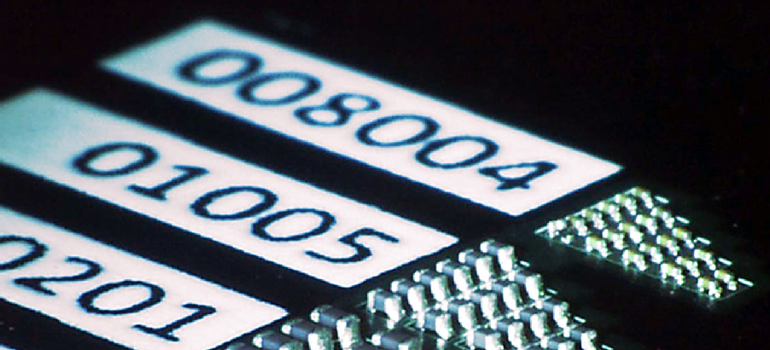

While a resistor is conceptually simple, each has non-ideal characteristics, as no device is perfect. In the case of a chip resistor, said device will have capacitive and inductive parasitics. The effect of the capacitance can be modeled as a capacitor in parallel with the resistor, and the effect of inductance as an inductor in series with the resistor. Parasitic capacitance of chip resistors tends to be quite small (<1 pF), leading to low frequency (near DC) impedance that is generally >100 GΩ, which will have minimal effect on the resistance value of all but the highest resistance value resistors. This effect is generally compensated during the design process but should be understood as the compensation likely changes with frequency. With increasing frequency the impedance associated with the parasitic capacitance is reduced. This effect can be significant when capacitive parasitic impedance is similar to, or less than, the nominal resistance value. For example, in the case of a parasitic capacitance of 1 pF, the associated capacitive impedance at 100 MHz will be about 100 Ω. This parasitic could affect the actual impedance by as much as 33% in the case of a 50 Ω termination resistor at 100 MHz. Again, this is usually compensated in the design, but it is important to understand as the effect changes with frequency and with resistance value. The inductive parasitic may also be important at high frequencies. For example, a parasitic inductance as low as 10 nH at 100 MHz will contribute about 50 Ω in to the impedance of the resistor. Again, this is compensated for during the design process in order to achieve proper performance over a range of frequencies, and thus is important to the understanding of the frequency range appropriate to the device selected for your circuit and your situation, as the combined effect of the parasitics upon overall impedance changes with changing frequency.

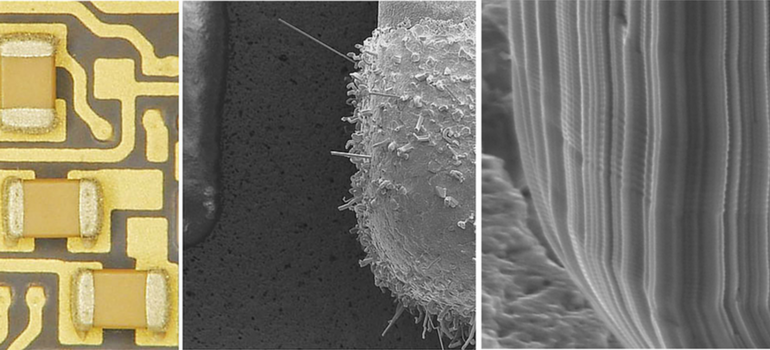

Skin Effect

As frequency is increased in an AC circuit, current flows more and more toward the periphery of the conductor through which it flows. This is called the skin effect, and may result in increased impedance as frequency is increased. The current density in a conductor (or resistor element) decreases from the outside to the inside of the conductor according to the relation:

where:

- Jd is the current density at depth d into the conductor (A/m2)

- JS is the current density at the surface (s) of the conductor (A/m2)

- d is the depth into the conductor (m)

δ is the skin depth of the material comprising the conductor (m) as defined by the relation:

where:

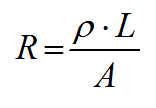

- ρ is the resistivity of the conductor or resistor material (Ω-m)

- f is frequency (Hz)

- µ0 is the magnetic permeability of free space (1.257×10−6 H/m)

- µr is the magnetic permeability of the conductor or resistor material (H/m)

Skin depth tells you the depth at which the effective conductivity of a material is reduced to 1/e (~37%) of its full value at the exterior skin. As frequency and/or magnetic permeability are increased, skin depth δ decreases at a half power rate, and as resistivity increases, δ increases at a half power rate. This is important mainly in thick film resistors where the thickness of the resistor element(s) tends to be considerably greater than for thin film analogs, making thick film resistors generally more susceptible to increased impedance at high frequency as compared to thin film resistors due to the skin effect. Additionally, perimeter geometries of printed thick film resistor traces tend to be less consistent compared to thin film resistor traces, and as the current is forced toward the outer portion of the conductor, the current path becomes more tortuous, further increasing apparent impedance at elevated frequencies in thick film resistors. Magnetic permeabilities and resistivities of the resistor trace materials are also important considerations. To minimize the skin effect (i.e., to maximize δ), it is generally preferable to use high resistivity, low magnetic permeability materials, and to understand these values at the frequencies and fields of your application as they may change greatly with changing field or frequency.

Summary

Resistors have myriad applications in electronic circuits. For gain setting, it is important to make sure that precision and TCR are appropriate for your application, and using a resistor network, or precision resistors, or trimmable resistors is appropriate. Additionally, to avoid temperature-related resistance change, as well as other signal noise related effects, it is important to design for minimal ΔT both between resistor terminals and between individual resistors in your circuit as well as to keep the overall temperature of the resistors as low as practicable. It is also important to understand how parasitics affect resistor performance as frequency is changed, and to minimize parasitics in a manner that is cost effective for your application through both device selection and circuit design. For high frequency applications, skin effect may also become important, and the potential geometric advantages of thin film resistors over thick film resistors, as well as the properties of the resistor materials used in the device selected, should be carefully considered. Until next time…TTFN!